Verilog code for Half Adder with Testbench

|

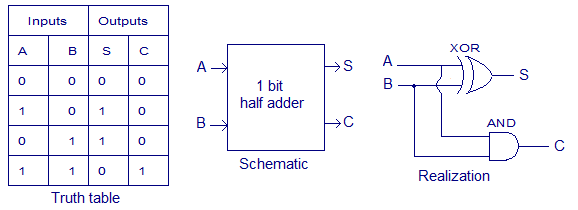

| Half Adder |

module half_adder ( A,B,S,C );

output S ;

output C ;

input A ;

input B ;

assign S = A ^ B;

assign C = A & B;

endmodule

Testbench

module halfadder_tb;

wire t_s,t_c;

reg t_a, t_b;

orgate my_gate( .a(t_a), .b(t_b), .s(t_s), .c(t_c));

initial begin

$monitor(t_a, t_b, t_s,t_c);

t_a = 1'b0;

t_b = 1'b0;

#5

t_a = 1'b0;

t_b = 1'b1;

#5

t_a = 1'b1;

t_a = 1'b1;

t_b = 1'b0;

#5

#5

t_a = 1'b1;

t_b = 1'b1;

endendmodule

Comments

Post a Comment