VHDL code for Half adder with Test Bench

Half Adder

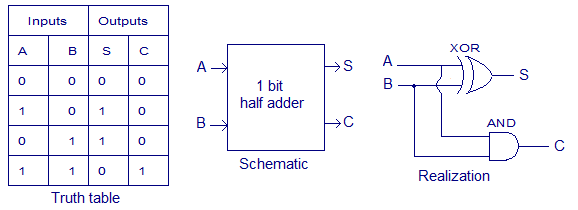

Half adder is a combinational arithmetic circuit that adds two numbers and produces a sum bit (S) and carry bit (C) as the output. If A and B are the input bits, then sum bit (S) is the X-OR of A and B and the carry bit (C) will be the AND of A and B. From this it is clear that a half adder circuit can be easily constructed using one X-OR gate and one AND gate. Half adder is the simplest of all adder circuit, but it has a major disadvantage. The half adder can add only two input bits (A and B) and has nothing to do with the carry if there is any in the input. So if the input to a half adder have a carry, then it will be neglected it and adds only the A and B bits. That means the binary addition process is not complete and that’s why it is called a half adder. The truth table, schematic representation and XOR//AND realization of a half adder are shown in the figure below.

CODE

ENTITY half_adder IS --- Half Adder

PORT(a,b:in std_logic; s,c :OUT std_logic);

END half_adder;

ARCHITECTURE half_adder_beh OF half_adder IS

BEGIN

s <= a XOR b; -- Implements Sum for Half Adder

c <= a AND b; -- Implements Carry for Half Adder

END half_adder_beh; Test Bench

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity or_tb is

-- Port ( );

end or_tb;

architecture Behavioral of or_tb is--Component name and entity's name must be same--ports must be same component half_adder is

Port (a,b:in std_logic;

s,c: out std_logic );

end component;

--inputs

signal a: std_logic:= '0';

signal b: std_logic:= '0';

--outputs

signal c : std_logic;signal s : std_logic; begin

uut: half_adder PORT MAP(a=>a,b=>b,c=>c,s=>s);

--Stimulus Process

stim_proc:process

begin

wait for 10ns;

a<='1';

b<='0';

wait for 10ns;

a<='0';

b<='1'; wait for 10ns;

end process;

end Behavioral;

Well explained

ReplyDeleteHelped a lot.tq

ReplyDeleteop bhai. lab bacha li

ReplyDelete